Intel’s process nodes will go from 20A this year to 14A by 2027

Intel will debut its 18A process node next year

But starting with its 20A production later this year, Intel will have a bit of a head start on TSMC and Samsung Foundry with a key feature that the American chipmaker calls PowerVia (also known as known as backside power delivery). TSMC is expected to use this technology with its N2P node which it will use starting in 2026. Samsung Foundry is supposedly going to use backside power delivery on a particular node launching next year, although Samsung Foundry has not confirmed this.

So what is PowerVia? Most of the small wires that deliver power to a chip are found on top of all of the layers that make up a silicon component. As these chips become more powerful and complex, the wires on top that connect to power sources are competing with the wires that connect components. This results in wasted power and low efficiency.

PowerVia moves the wires bringing power to the chips to the backside of the chip. As a result, clock speeds can increase by 6% resulting in greater performance. Add to that the increase in performance delivered by using a more advanced process node, and the result is a more powerful chip used to run a more powerful device.

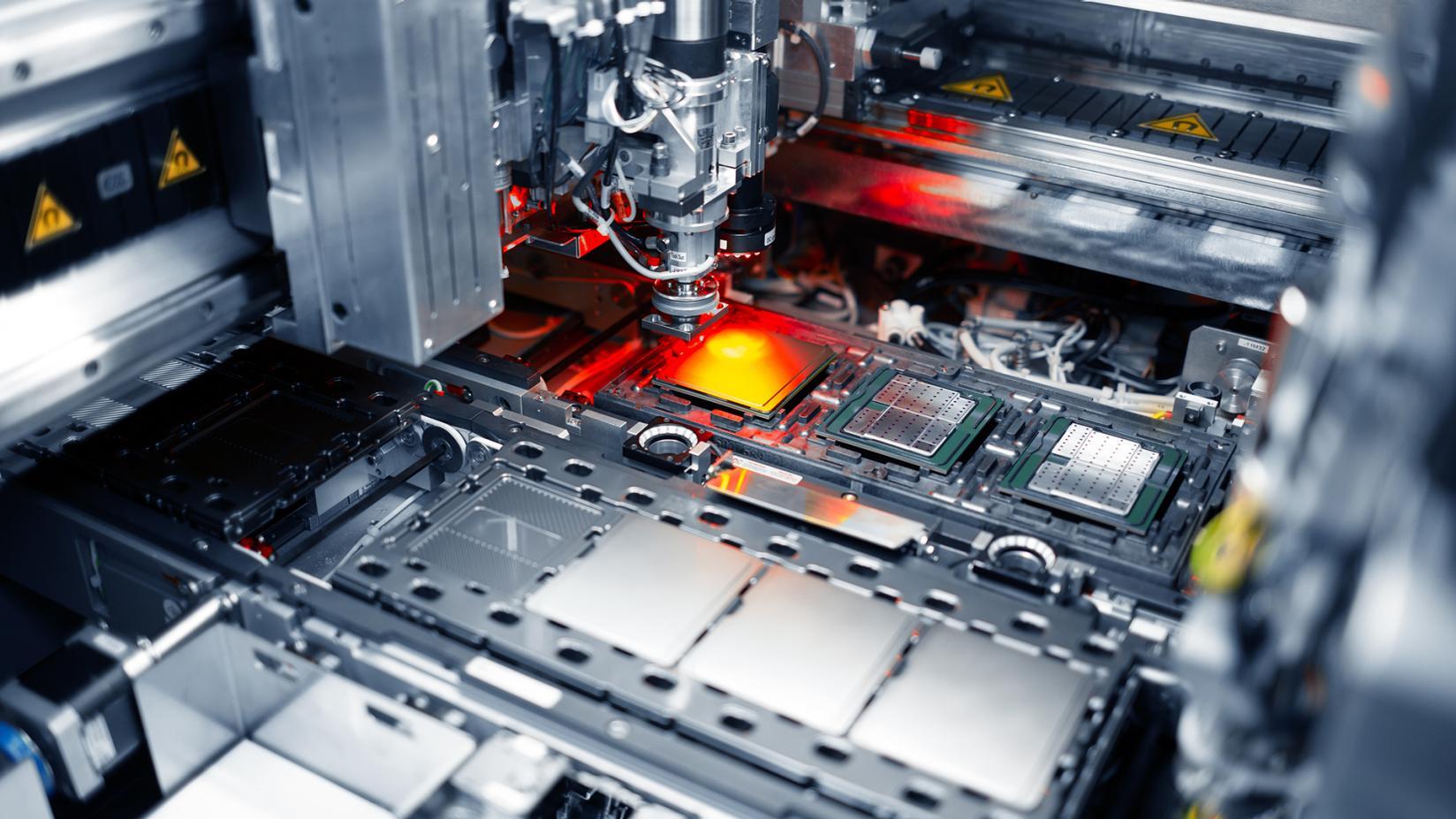

Intel is first to take delivery of its High-NA Extreme Ultraviolet Lithography machine

Intel CEO Gelsinger said, “I’ve bet the whole company on 18A.” Intel expects that the performance and efficiency of its 18A node will top TSMC’s best. Intel also inked a deal with Arm allowing Arm’s chip-designing customers to have low-power SoCs built using Intel’s 18A process node. Last month, Intel agreed to build a custom chip for Microsoft using its 18A process. Four unnamed large companies (it’s not clear whether Microsoft is one of the four) have signed on to have Intel produce their chips using the 18A process.

The older EUV machines have an aperture of .33 (equivalent to a resolution of 13nm), and the High-NA machines have an aperture of .55 (equivalent to a resolution of 8nm). With a higher resolution pattern transferred to a wafer, the foundry could avoid having to run a wafer through the EUV machine twice to add additional features saving both time and money. While TSMC and Samsung Foundry have both ordered one of the High-NA machines from ASML, Intel will probably get to use the time-saving lithography machine first.